# LEARNING MATERIAL OF DIGITAL ELECTRONICS & MICROPROCESSOR PREPARED BY – ER. BISWARANJAN JENA

&

ER. SASWATI SANGHAMITRA PRADHAN

Basics of Digital Electronics:

## Number System

- 1 Decimal Number System.

- (2) Binary Number System.

- 3) Octal Number System

- (4) Hexadecimal Number System

- ① Decimal Number System:

Lymans 10. So this System has 10

distinct digits or symbols

ie 0123456789.

-> In desimal number system the base is 10.

$$= 7 \times 10^{3} + 6 \times 10^{2} + 3 \times 10^{4} + 9 \times 10^{6}$$

Positional weight of the decread number system.

In general any number in decimal number system can be written as,  $N = a_0 \times 10^{0} + a_{11} \times 10^{0} + \dots + a_{21} \times 10^{2} + a_{11} \times 10^{1} + \dots + a_{21} \times 10^{2} + a_{11} \times 10^{1} + \dots + a_{21} \times 10^{2} + a_{11} \times 10^{1} + \dots + a_{21} \times 10^{2} + a_{11} \times 10^{1} + \dots + a_{21} \times 10^{2} + a_{11} \times 10^{2} + \dots + a_{21} \times 10^{2} + \dots +$

- > The powers realised to 10 depends on the position of coefficient.

- -> The positional power raised to 10, which is known as the readix or base of this decimal number system

epeneral form of any number system can be written as,

$N = a_{n} \times (\pi)^{n} + a_{n-1} \times (\pi)^{n-1} + \dots + a_{1} \times (\pi)^{1} + a_{n-1} \times (\pi)^{1}$

The weighted enefficient are an to a\_m.

a\_m → coefficient is called LSD

(Least Significant Digit).

an -> is known as the most significant digit (MSD).

2) Binary Number System: -

-> Binary numbers system consists of 2 distinct elements or digite the <u>C 1/1</u> only.

-> Base on Radix of the number system

is 2 \*

.. ) The digit O & 1 is known as bits.

$$\frac{e^{-g}}{1} = \left(\frac{10}{1} \cdot \frac{10}{1} \cdot \frac{10}{1}\right)_{2}$$

,  $\left(\frac{10}{10} \cdot \frac{10}{10}\right)_{2}$

bit

The binary numbers are pronounced in the

following manners.

o' is pronounced as "teno".

10' is " one zeno

(11 is as one one not

| ing of<br>Digital | the Binary<br>Number | Number :-<br>Binary Number |

|-------------------|----------------------|----------------------------|

| 0                 |                      | . O                        |

| 4-                |                      | <u>1</u>                   |

| 2                 | - 8                  | 1 0                        |

| 3                 | 39                   | 1.1                        |

| ч                 |                      | t 0 0                      |

| 5                 | 16 65<br>25          | 101                        |

| 6                 |                      | 110                        |

| 7.                | = -                  | 1 1 1                      |

| 8                 |                      | 1 000                      |

| 9                 | 3                    | 1001                       |

| 10                | -                    | 1010                       |

| 1.1               |                      | 1011                       |

| 12                | 64)                  | 1100                       |

| 1.3               |                      | 1101.                      |

| 14                | 1                    | 1110                       |

| 15                |                      | 1111                       |

| 16                |                      | 1 0000                     |

| 1.4-              |                      | 10001                      |

| 18                |                      | 10010                      |

| 19                | 2                    | 10014                      |

| .20               |                      | 10100.                     |

| 21                |                      | 10101.                     |

医面侧

eg: (10110), position of bits.  $(10110)_{2}^{7LSS} = 1 \times 2^{4} + 1 \times 2^{2} + 1 \times 2^{1}$ = 16 + 4 + 2 = (22) -) It is very exential to show the suffix to the numbers which indicates the base of the number system. ( ) find the decimal equivalent of the binary number (11011001.0101). Solo: - (11011001.0101) => 1 x 2 + 1 x 2 + 1 x 2 + 1 x 2 + 1 x 2 + 1 x 2 + + 1 × 2 - + 1 × 2 - 4 => 128 + 64 + 16 + 8 + 1 + 1 + 16 => (217. 3125)10-Practice Question ! -(11), 1 (101), , (1010), (9 (10011), (5) (1010)2 ( (1010-11), ( (1011-01), , ( (111-11),

78 4

| Octal  | namben | System :-  |         |      |      |

|--------|--------|------------|---------|------|------|

| The    | base   | or mudix   | of the  | odal | numb |

| system | is     | 8. (Octal  | means   | 8) . |      |

| > Die  | gits o | r elemente | will be |      |      |

-> Digits or elements will be,

| Decimal      |      |

|--------------|------|

| Decimal Octo | ed . |

| 0            |      |

| 1            | 61   |

| 2 2          |      |

|              |      |

| Ч            | 18   |

| 5            |      |

| 6 6          |      |

| 7- 7-        |      |

| 8 10         |      |

| 9            |      |

| 10 12.       |      |

| 11 13        |      |

| 12 14        |      |

| 13           |      |

| 14 16        |      |

15

eg: - (246) Down to the presence of '8'. This is not on octal number system (736)8 V 1940s not an octal number. S: The decimal Equivalent of octal number Ans: - (24) = 2 x 8 + 4 x 8 . = 16 + 4 = (20) 10 8) (7126.45) = (?) 8010: - ( 7128. 45) = 7 x 83 + 1 x 8 + 2 x 8 + 6 x 8 + 4 x 8 + 5 x 8 2 = 512 x7 4 64x1+ 16+6+4x0-175 + 5 x 0 0156 3584 + 64 + 16 + 6 +0.5 +0078 = (3670 · 578) Priactices-(i) (37), (ii) (311), (iii) (125.7), (iv) (100.21) 8 (v) (217.31) 8.

Hexadecimal Number System:--> In this system the madix or base is 16 -> It consists of 16 distinct symbol or element. Hexadecimal Delimal Number number System system.

€9:- (ABC)16 , (123)16, (12A)16 (9 43)16. fractional: (AB1. CD) (123 A) 16. -> Decimal Equivalent of Hexadecimal number, (ABC)16 = Ax10162+ Bx161+ Cx160 = 10 × 162 + 11 × 16 + 12 × 160 = 2560 + 176 + 12 = (2748)10 29: (AOF9. OEB) = 10 × 163+ (0 × 162) +(15×16) + (9x16°) + (0x161) + (14x162) + (11 ×16-3) = (41209.0572)10 Convention of Number System:-Decimal - Binary Binary - > Desimol Octal -> Decimal - Decimal -> Octal. Hexadesimal -> Desimal . | Desimal -> Hexadesimal Long Division method. positional weight -> Octal to Binarry method. > Binary to Octal 7 Binary to Hexadecimal -> Octob to Hexadecimal

Interpretable Decimal

$$\rightarrow$$

Binary  $\stackrel{?}{\circ}$  -

A)  $(35)_{10} = (?)_{2}$

A)  $2 | 35$

$2 | 17 - 1$

$2 | 8 - 1$

$2 | 9 - 0$

$2 | 1 - 1$

$3 | 9 - 0$

$4 | 1 - 0$

$4 | 1 - 0$

$4 | 1 - 0$

$4 | 1 - 0$

$4 | 1 - 0$

$4 | 1 - 0$

$4 | 1 - 0$

$4 | 1 - 0$

$4 | 1 - 0$

$4 | 1 - 0$

$4 | 1 - 0$

$4 | 1 - 0$

$4 | 1 - 0$

$4 | 1 - 0$

$4 | 1 - 0$

$4 | 1 - 0$

$4 | 1 - 0$

$4 | 1 - 0$

$4 | 1 - 0$

$4 | 1 - 0$

$4 | 1 - 0$

$4 | 1 - 0$

$4 | 1 - 0$

$4 | 1 - 0$

$4 | 1 - 0$

$4 | 1 - 0$

$4 | 1 - 0$

$4 | 1 - 0$

$4 | 1 - 0$

$4 | 1 - 0$

$4 | 1 - 0$

$4 | 1 - 0$

$4 | 1 - 0$

$4 | 1 - 0$

$4 | 1 - 0$

$4 | 1 - 0$

$4 | 1 - 0$

$4 | 1 - 0$

$4 | 1 - 0$

$4 | 1 - 0$

$4 | 1 - 0$

$4 | 1 - 0$

$4 | 1 - 0$

$4 | 1 - 0$

$4 | 1 - 0$

$4 | 1 - 0$

$4 | 1 - 0$

$4 | 1 - 0$

$4 | 1 - 0$

$4 | 1 - 0$

$4 | 1 - 0$

$4 | 1 - 0$

$4 | 1 - 0$

$4 | 1 - 0$

$4 | 1 - 0$

$4 | 1 - 0$

$4 | 1 - 0$

$4 | 1 - 0$

$4 | 1 - 0$

$4 | 1 - 0$

$4 | 1 - 0$

$4 | 1 - 0$

$4 | 1 - 0$

$4 | 1 - 0$

$4 | 1 - 0$

$4 | 1 - 0$

$4 | 1 - 0$

$4 | 1 - 0$

$4 | 1 - 0$

$4 | 1 - 0$

$4 | 1 - 0$

$4 | 1 - 0$

$4 | 1 - 0$

$4 | 1 - 0$

$4 | 1 - 0$

$4 | 1 - 0$

$4 | 1 - 0$

$4 | 1 - 0$

$4 | 1 - 0$

$4 | 1 - 0$

$4 | 1 - 0$

$4 | 1 - 0$

$4 | 1 - 0$

$4 | 1 - 0$

$4 | 1 - 0$

$4 | 1 - 0$

$4 | 1 - 0$

$4 | 1 - 0$

$4 | 1 - 0$

$4 | 1 - 0$

$4 | 1 - 0$

$4 | 1 - 0$

$4 | 1 - 0$

$4 | 1 - 0$

$4 | 1 - 0$

$4 | 1 - 0$

$4 | 1 - 0$

$4 | 1 - 0$

$4 | 1 - 0$

$4 | 1 - 0$

$4 | 1 - 0$

$4 | 1 - 0$

$4 | 1 - 0$

$4 | 1 - 0$

$4 | 1 - 0$

$4 | 1 - 0$

$4 | 1 - 0$

$4 | 1 - 0$

$4 | 1 - 0$

$4 | 1 - 0$

$4 | 1 - 0$

$4 | 1 - 0$

$4 | 1 - 0$

$4 | 1 - 0$

$4 | 1 - 0$

$4 | 1 - 0$

$4 | 1 - 0$

$4 | 1 - 0$

$4 | 1 - 0$

$4 | 1 - 0$

$4 | 1 - 0$

$4 | 1 - 0$

$4 | 1 - 0$

$4 | 1 - 0$

$4 | 1 - 0$

$4 | 1 - 0$

$4 | 1 - 0$

$4 | 1 - 0$

$4 | 1 - 0$

$4 | 1 - 0$

$4 | 1 - 0$

$4 | 1 - 0$

$4 | 1 - 0$

$4 | 1 - 0$

$4 | 1 - 0$

$4 | 1 - 0$

$4 | 1 - 0$

$4 | 1 - 0$

$4 | 1 - 0$

$4 | 1 - 0$

$4 | 1 - 0$

$4 | 1 - 0$

$4 | 1 - 0$

$4 | 1 - 0$

$4 | 1 - 0$

$4 | 1 - 0$

$4 | 1 - 0$

$4 | 1 - 0$

$4 | 1 - 0$

$4 | 1 - 0$

$4 | 1 - 0$

$4 | 1 - 0$

$4 | 1 - 0$

$4 | 1 - 0$

$4 | 1 - 0$

$4 | 1 - 0$

$4 | 1 - 0$

$4 | 1 - 0$

$4 |$

$$A_{M} := 8 | 12.76 |$$

$8 | 159 = 4.$

$8 | 181 = 7$

$8 | 2 = 3$

$0 = 2$

$$Ans: -16 | 2598$$

$16 | 162 \longrightarrow 6 \bigcirc 6$

$0.6+5 \times 16 = 10.8$

$16 | 162 \longrightarrow 2$

$0.8 \times 16 = 12.8$

$0.8 \times 16 = 12.8$

$0.8 \times 16 = 12.8$

## Application : -

- is 8 = 23, so every 3-bit group of binary can be represented by an octal digit.

- -> An octal number in the 1/3 rd the length of the corresponding binary number

- -> In computer work binarry mumbers with up to 64-bits are not uncommon.

- These binary numbers do not always represent a numerical quantity, they often represent some type of code, which conveys non-numerical information

- A binary number might regonerent

- (a) the actual numerical data

- (b) the numbers corresponding to a location (address) in memory.

- (1) an instruction code.

- (d) a rade expressing alphabetic & other mon-numerical other non-numerical other non-numerical other non-

- (e) a group of bits representing the Status of devices interal or external to devices.

- of the operations of the system.

- The digital circuit and systems work structly in binarry

- -> A 4-bit group is called nibble.

- "> Since computer words come in 8 bit,

16 bit, 32 bit and 80 on, that 18,

multiples of 4-bits, they can be

easily represented in hexadecimal.

- for human communications with computer.

Hexadermal: -

> Since the base is 16 = 24. every combination can be represented by one hexadecimal digit

1233 202

0.202 ×8 = 1 = 616

0 . 616 x 8 = 4.928

O 7.424

3-392

3-136.

M3

1233

8 154 -1

8 2 --- 3

0 --- 2

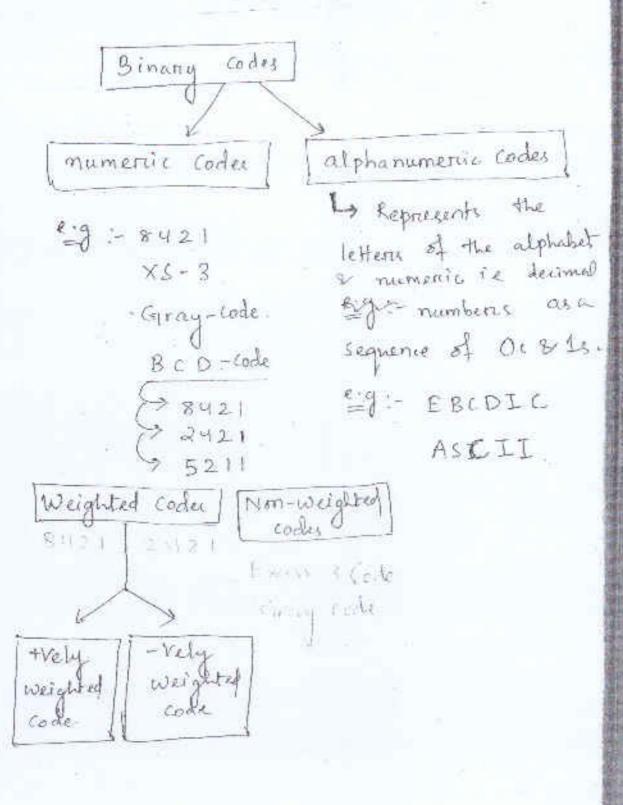

## BIPLARY CODES

# Positively-weighted codes:-

Positively - weighted cake are those in which all the weight assigned to the binary digits are positive.

-> There are only 14 positively weighted codes.

To every + vely weighted codes, the first weight must be weight must be 1, 2nd weight must be either 1 or 2, and the sum of the weight must be either 1 or 2, and the sum of the weight must be equal to or greaten than 9.

€g:- 8421, 2421, 5211,3321,4311

Megatinely weighted codes: -

Here the weighter assigned to the binning digits are negative.

eg: 642-3,631-1,84-21,74-2-1

Ennon Detecting and Error Correcting codes:

-> The codes which allow only error defection are called error defecting rades

=9:- shift counter Code To From Detecting

2 out-of 5, 63210 codes Teches

Error correcting codes:

Codes which allow error defection as well as error correction are called error correcting codes.

Eg:- Hamming sodes Sequential codes:-

A sequential code is one, in which each succeeding code word is one binary number greater than it's preceding code word.

Such a rode facilitates mathematical manipulation of data: The

Eg: - 8421, XS-3 are Segmential.

5211, 2421 and 542-3 are mon. Segmential.

Self complementing roder:For a rode to be self-complementing:

the sum of all it's weights must be q.

Solt complementing positively weighted sinter.

There are 13 negatively-weighted selfcomplementing codes. cyclic code are those in which each successive code word differs from the preceding code in only one bit position. They are also called unit distance codes.

-> Advantage - They minimize transitional errors or eflashing.

-> Gray code is a cyclic code:

Reflective Code is a binary number.

In which the 'n' least significant bits for code coords 2nd through 2nti-1 are the mirror image of those for '0' through 2n-1. The gray code is a reflective code.

18 Complement Representation: -The 1's complement of a binary number obtained by converting each obit of the binary number to a 1, and each 16 by a '0'. =8? - find the 1's complement of the binary number 1011101 is 9 Ans:- 1011101 ---- > 0100010 2's complement Representation: The 2's complement of a binary number is obtained by taking 1's complement of the number and adding I to the least significant bit position. S: - find the 2's complement of (25) 10 = (11001) in given 11001 15 00110

The 2's complement of (11001) is (

other method !-The another method of obtaining the 2's complement of a binarry number is to. scan the number from Right to left and complement all bits appearing after the 11+ scan of a (1'. 11001 (L) 1 (B) (42)10 = (101010)2 2'8 010110 1st one -> 1000 1001.  $16 \left[ 9 - 12 \left( c \right) , \frac{16}{80} - \frac{16}{13} \right]$ 160 3:16/813

18

11209 ,0572 16 41209 / 2575 16/41209 92 16 2575 - 9. 120 16 [160 -- 15 (E) 16 (10 10 (A 0572×16 = 16 2575 ) 169 (DEDE AAE) 001101 1111 0010 1111.1010 1010 1110

Representation of Signed Number using 2's (on 1's) Complement method.

- 1) If the number is positive, the magnitude is represented in it's true binary form and a sign bit 'O' is placed in front of the MSB.

- 2) If the number is negative, the magnitude is presented in it's 2'3 (or 1's) complement form and a sign bit 1 is placed in front of the MSB.

- > The 2's (on 1's) complement operation on a signed number will change positive number to a negative number and vice versa.

- is the same as the process used to convert true binary to complement.

$$e \cdot g \cdot - +51 = 0 \cdot 11 \cdot 00 \cdot 11$$

$$= \frac{1}{51} \cdot \frac{1}{$$

(2's complement).

-51 = [1.00 1100] (1's complement 218 form) Sign bit Magnitude tude Q: Each of the following number ix a signed binary number . Determine the decimal value in each case if they are in, ni tude (1) Sign - magnifude form. plement (ii) 2's complement form (前) 11名 " 4ns;- (a) 01101 (b) 010111 (c) 10111 (4) 1101010. Greven Number Signed-mag-form 2'8 1's 01101 binary +23 +23 010111 + 23 10111 - 7-- UZ . - 22 . - 21 -1101010 -7 101010 -> 010101 01101 28 0010 0111 -> 1000 1001 10011

- To Subtract using 2's (or 1's) complement method:

- O To subtract using 28 complement method represent both the subtrachend and the minuend by the same number of bits.

- 2) Take the 2's complement of the subtrahend including the sign bit.

Keep the minuend in it's original form and add the 2's (on 1's) complement of the subtrahend to it.

- when the sign bit is a 0', the remaining bit represent mognitude

When the sign bit is '1', the remaining bits represent 2's on 1's complement of the number.

- The polarity of the signed number can be changed simply by performing the complement on the complete number.

erted Methods of obtaining the 2'x complement 8 28 of a number:-1 By obtaining 1's complement of the given number they changing all Os to Is de and 1s to 0s) and then adding 1. (2) By bubtracking the given or bit number N from 2" (3) Starting tot the LSB, copying down 5 each bit up to and incluiding the first 1 bit encountered and complementing the remaining brits . (8.1) Express - ut in 8-bit 2's complement from . Ang! - (OD101) = 4510 22 -- 1 2 111-+ 45 = 000+0+0+. 2 5 -1 2 [2 -0] +45 = (01101) +45 = 000 0 1101

2's complement Arithmetic:

The 0's complement system is used to represent negative numbers using modulus arithmetic.

The coord length of a computer is fixed.

Ar

That means, if a 4-bit number is fixed.

That means, if a 4-bit number is added to another 4 bit number the result will be only of 4 bit. Carry if any from the fourth bit will overflow. This is called the modulus arithmetic.

2's complemented arithmetic.

Ans: +14 = 00001110 -14 = 111100001 (1/3) -14 = 11110010 (2/3) +46 = 00101110 -14 = 11110010 (2/3) complement -14 = 11110010 (2/3)

ignore the corry.

8.2) Subtract 2 from 5 wing 4- hit 2's complement withmetic. +5 = 0101+2 = 0010 ho -2 = 1101(18)-2 = 1110(2'8)QE!  $+\frac{1}{2} = 0101$ (DOOII = (+3) (Am) ignone. Q.3) Subtract -2 from 5 using 4 bit 2's complement arithmetic. 2 = 10 15 = 0101. -2=110 -0 = 1010 +2 = 0101 (1/3) -2 = 0110 +2 = 0 110 (2/8) +2=1001 1010 5 - (-2) = (7). 0101 0101 0++ 0110 1010 1011 1111 -2 = 1110 (2'8 +2 = \$000 \ complex yo10

(3.4) Add -75 to +26 asing 8-6:1-2's complement anotheretic. Ans:- + 75 + 26 = -49 +35 = 01001011 2 37--75 = 10110101 (2's) +26 = 000 11010 -75-10110101 (D1001111 2 (No carry) magnitude of 2's complement form is = 0 1001111 0 110000

(-49)

1 10001

WIII.

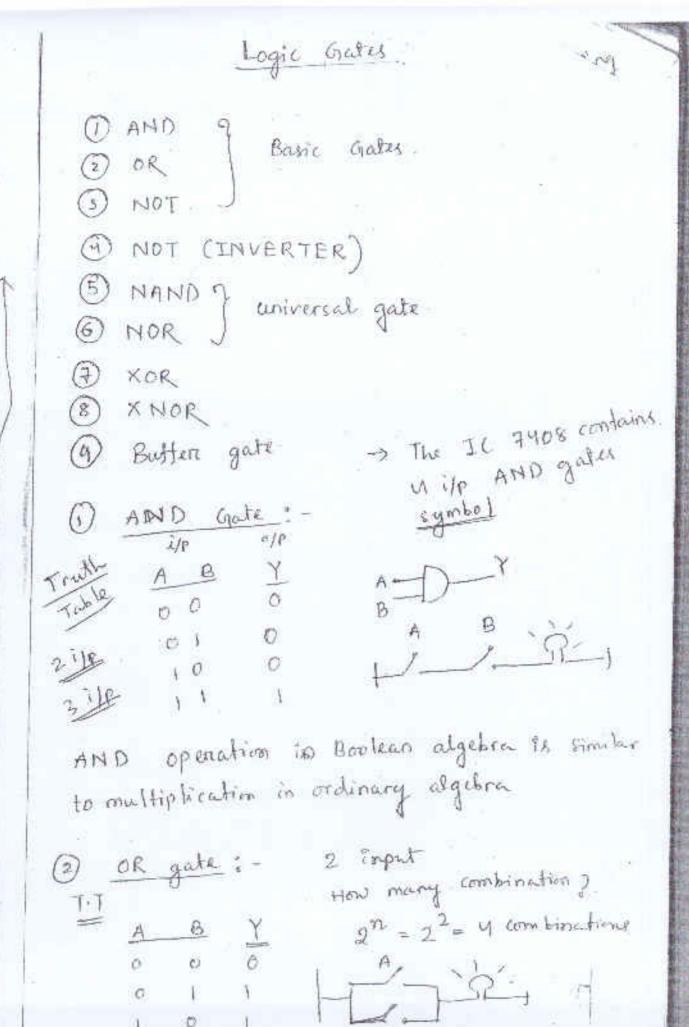

-> All the gates can be designed using the NAND & NOR gate. So this is called Universal gate.

XOR Gates: -

### Truth Table

| Α | B   | Y   |

|---|-----|-----|

| 0 | 0   | 0   |

| 0 | 1   |     |

| 1 | 0   | . 1 |

| 1 | · F | 0   |

XNOR Gates :-

## Truth Table ! -

| ( A |    | 12 | 14_ |

|-----|----|----|-----|

| 0   |    | 0  | 1   |

| 1   | b  | 1  | 0   |

|     | j. | 0  | 0   |

| 1   | 1  | 4  | 1 1 |

1 Logic Gates are the fundamental building block of digital system.

#### AND

- -> The IC 7408 contains four 1/p AND gates.

- -> The IC 7411 contains 3-1/p AND gates

- -> IC 7421 contains 4-1/p AMD gates.

What is Logic Gates?

Ami- Logic gates are electronic circuit

because they are made up of a number of

electronic devices and components.

- -> They are usually embedded in a large scale integrated circuit (LSI).

- > Very large scale integrated circuit (VLI) along with a large number of other devices.

- -> Each gate is dedicated to a specific logic operation

- > dogic gales are also constructed in

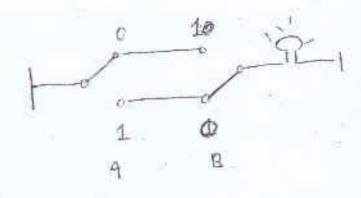

Lagie terels done dogic tre logic 103 -> Voltage levels represent Logic I and Logic O. -> + Ve logic -> 15V -> Logic D -> - Ve logic -> Loner of the two voltages -> Higher of the two volterys represents the Logic I of represents the logic O OR: IC-7432 contains four two-1/p 1) or gates. NOT: - Il 7404. contains six inverters. 35

(Iniversal Gate (NOR, MAND):--> Bother NAND and NOR gates we can XO penform all the three ban's logic function. NAND. OMAN ONI-OUT A tribted CONF- DI gates. IC-7410 contains 3 three-ip NAND gates IC-7420 contains & four-ip NAND gates IC-7430 ". 1,8-11p NAND gate NOR Gates :-NOR MEAN NOT+ OR -> The O/p is 'I high when both the i/ps are low (0). If any of the i/p is high the Ofp is zero. つり -> For 3 i/p case also of all the i/ps are "O' low then the 0/p is high other wise the opp in tero. -> The I.C-7402 contains, four two i/p MOR gales. -> The IC-7427 con-lains. three 3-1/8 NOR gate.

NOR gale:

one of its two i/ps assumes a logic-1 ords.

When both the i/ps are logic-0 or both

the i/ps logic-1 State the 0/p assumes logic-0

-> since an x-or gate produce an op-1 only when the ipps are not equal, it is called as anti-coincidence gate or inequality detector

Ci

- -> Three or more variable x-or gates

do not exist.

- -> II IC 7486 confains 4 x-or gates.

> IC 74C86 " M XDR gates.

CMOS.

- -> High speed (MOS IC 74HC86 contains 4-xor gates

X-NOR :--> In equality defector. -> commaide gate: -> IC 79LS266 IL 74(266. IC 74 HC266 confains four each X-NOR gates. Realize AND, OR, MDT operations using NAND & NOR gates: a) Design a AMB gate using NAMD AND :gale? Ans :-2 1/p MAND gate

ANI

Α.

Ar

A

A

Com

Lo

ト

A

. . . . . . .

H

1

\_

0

Т

```

Boolean Algebra ---

( ) to by . W

Of daw

AND daw

A+0 = A

A. 0 = 0 (Null Law)

A+1=1

A-1 = A (Identity daw).

A+A = A

A. A = A:

A+A =1

A. A = 0

Commutative Law: -

A+B=B+A , A+B+C=B+C+A=C+A+B

Law-1

A.B. B.A., A.B.C = B.C.A = C.A.B

Law-2

= B A . C .

Associative Law: -

The associative laws allows grouping of

the variables. There are two associative but.

Law-1 (A+B) +C = A+(B+C)

Law-2 (A.B) C = A (B.C)

A (BCD) = (ABC) D = (AB) CCD)

Distributive Law: -

Law-1: A(B+c) = AB+AC.

The distributive laws allows factorising on

multiplying on multiplying out of expressions.

```

ABC(DIE) = ABCD + ABCE.

AB (CDIEF) = ABCD + ABEF.

A(B+1) = AB +AC

Law-2 :-

A+BC = (A+B) (A+C).

Redundant Literal Rule (RLR): -

Law-1: A+AB = A+B

Law-2 :- A (A+B) = AB.

Idempotence daws: -

daw-1 :- A : A = A.

1.60 -2 ? A+A = A

Absorption Law: -

daw -1: A+A·B=A.

Law -2: A (A+B) = A.

-> A + A. any term = A.

> A (A+ Any term) = A.

Indo

Theo

Theo

This

P

of 1

E \*

Trans

Theo

Demo

Lan

Law

1 -

d.

9 .

4

### Induced factor Theorem !-

Theorem 1: AB+AC+BC = AB+AC

Theorem 2: A (A+B) (A+C) (B+C) = (A+B)(A+C)

This theorem can be extended to any number of variables.

eg: (A+B) (A+C) (B+C+D) = (A+B) (A+C)

Transposition Theorem: -

Theorem :- AB + AC = (A+C) (A+B)

Demorgan's Theorum: -

Law -1: A+B = AB

A+B+C+D+ .... = ABCD ...

Law-2: AB = A+B

ABCD ... = A+B+ C+D+ ...

1. Complement the entire given function

2. Change all the ANDS to ORS and all

the ORE to ANDS.

8. complement each of the individual

4. change all 0s to 1's and 1's to 0's

The procedure is called demonganisation or complementation of statching expressions.  $f\left(A,B,C,\cdots,0,1,+,\cdot\right)=f\left(\overline{A},\overline{B},\overline{C},\cdots,-1,0,\cdot,+\right)$

Shannon's Expansion Theorem:

$$f(A,B,C,...) = A \cdot f(1,B,C,...) + \overline{A}f(0,B,C...)$$

$f(A,B,C,...) = [A + f(0,B,C...)] + [\overline{A} + f(1,B,C,...)]$

B) Demorganite f = (A+B) (C+D)

8) Reduce the expression  $f = \overline{AB} + \overline{A} + \overline{AB}$

+ B) Reduce the expression f = A(B+C(AB+AC))

### Boolean functions and their representation; -

- 1) SOP (Sum of products) form.

- · @ POS ( Product of Swm) form

- (3) Truth Table form.

- B, L-) (4) Standard sum-of-products form.

- (3) Standard product of Sum form.

- (2) Venn diagram form.

- (7) Octal Designation.

- (8) Karnaugh map.

- $\begin{array}{c}

\underbrace{SOP} := \\

f(A,B,C) = \overline{A}B + \overline{B}C

\end{array}$

- 2) POS:f(A,B,C) = (A+B)(B+C)

Canonical Sum of product form,

- The product term which contains all the variables of the function either in complemented or uncomplemented form is called a minterm

- -> The minterms are often denoted as mo, m, m2

for a 3-variable function  $m_0 = \overline{ABC}$   $m_1 = \overline{ABC}$   $m_2 = \overline{ABC}$   $m_3 = \overline{ABC}$   $m_4 = \overline{ABC}$   $m_5 = \overline{ABC}$   $m_6 = \overline{ABC}$   $m_7 = \overline{ABC}$

=g: f (A,B,C) = m,+m2+m3+m5

There are the decimal coder of the function for which mintern for which f=1.

f(A,B,C)= \(\sum\_{(1,2,3,5)}\)

where  $\sum$  in represents the sum of all the mintern which decimal codes are given in the parenthetis.

- product of sums form or Canonical Products

of sum form.

- -> This is a desired by considering the combinations for which f=0.

- -> Each term to a sum of all Variables

- form of it has a value of 0 in the combination and appears in complemental

form if it has a value of I in the combination (A+B+1) A = 0 A = 1 B = 0 10 m C = 0 . f(A,B,C) = (A+B) (A+B). f(A,B,c) = (A+B+CT) (A+B+CT). (A+B+C)(A+B+C)(A+B+C)(A+B+C) The sum term which contains each of 'n' Variables in either complemented or uncomplemented form is called maxterm. -> The product of maxtern corresponding to the row for which f = 0. This is standard or conomical SOP form. -> Maxterm represented as Mo, M1, M2, M3 J(A,B,C) = MO. My. MG. MJ f (A,B,() = T M(0,4,6,7) It represents the product of all maxterns currous desimal code is given within the

$$f(A,B,c) = (\overline{A}+\overline{B}+c)(\overline{A}+\overline{B}+\overline{c})(A+B+c)$$

$$(A+B+\overline{c})$$

$$M_0 = (\overline{A}+\overline{B}+\overline{c}) = 0$$

$$M_1 = (\overline{A}+\overline{B}+\overline{c}) = 0$$

$$0+\overline{B}+0$$

$$A = 0$$

$$B = 1$$

$$c = 1$$

$$0 = \overline{A}$$

$$M_0 = (\overline{A}+\overline{B})$$

$$M_1 = \overline{A}$$

$$M_2 = \overline{A}$$

$$M_3 = A$$

$$M_4 = A$$

$$M_4 = A$$

$$M_5 = A$$

$$M_6 = A$$

$$M_1 = A$$

$$M_1 = A$$

$$M_2 = A$$

$$M_3 = A$$

$$M_4 = A$$

$$M_4 = A$$

$$M_5 = A$$

$$M_6 = A$$

$$M_1 = A$$

$$M_1 = A$$

$$M_2 = A$$

$$M_3 = A$$

$$M_4 = A$$

$$M$$

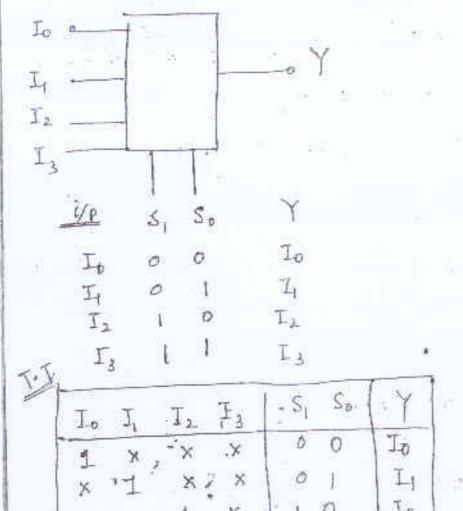

Design full adden wrong two half adder an or gate & write truth table. full Adder: -Sum= A@B@C carry = A (BOO) T (A OB) Cin + AB A B B O Cin = Sum cin +1 A (A() B) Cin +AB A @B & Cin Carry). (A)B) Cin Operation of multiplexur: - (Data Selector) -> multiplexur means Sharing. -> 2 types of multiplexing 1 (2) frequently multiplex Defo: - A multiplexer (MUX) or data selector is a logic circuit that accepts several data inputs and allows only one of them

at a i time to get through to the O/p. 1 -> The routing of the desired data i/p to the opp is controlled by selector i/p (Sometimes referred to as Address 2/ps) -> MUX acts like a digitally controlled multiposition switch. 1 2 i/p mux (2:1 Mux) 2) - 4 i/p MUX . (4:1 iMUX) 2:1 (m vx) Truth Table. Select line Expression . Y = 370+ ST. dogic Digram design!-

#### (in 4:1 MUX: -

x .x 1 X

x x · x · I3

$I_2$

I.3.

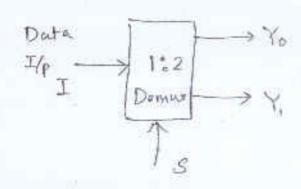

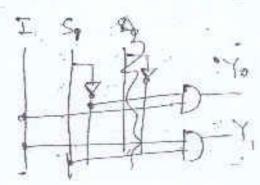

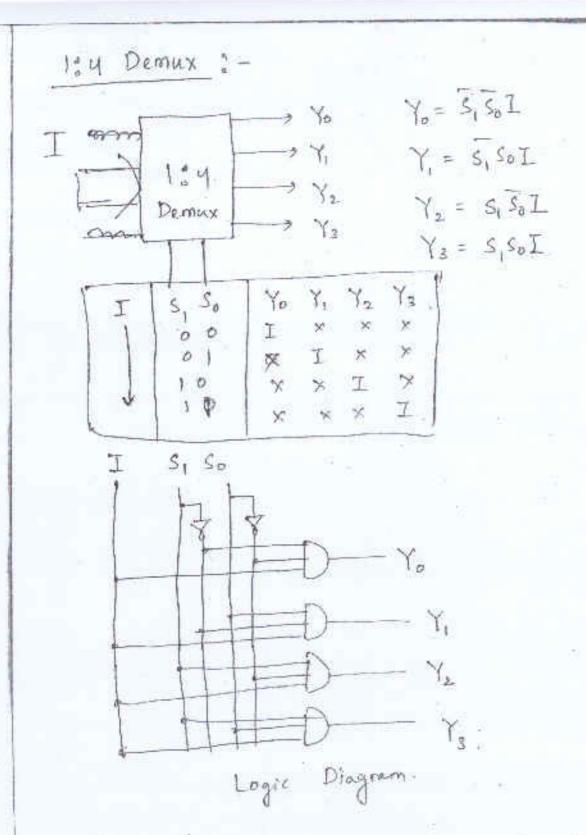

# Demultiplexen (DEMUX): (Data Distributors)

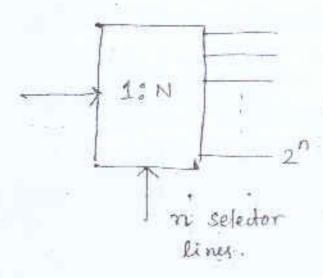

Det ":- It takes a single i/p and distribute it over several outputs.

> Demux is a 1:N(2") derive.

- 1:9 DEMVX .

- (2) 1:4 Demax

- (3) 1:8 Demux

| 1  |   | 200 | DE  | MUX   | DE 155 |

|----|---|-----|-----|-------|--------|

| -4 | 0 | 7   | 191 | LINIA |        |

| IS | 11/0 | Y |

|----|------|---|

| 10 | I    | × |

| 1  | X    | 1 |

## Electrical Engineering Material

- 1. Conducting materials

- 2. Semiconducting materials.

- 3. Insulating materials

- 4. Dielectric materials

- 5. Magnetic materials.

- 6. Material for special purposes.

# Magnetic Materials

- 1. In true duction.

- 2. classification

- 3. Diamagnetism

- 4. Para magnetism.

- 5. ferro magnifism

- 0.

- 6) Magnetisation curre

- 7) Hysterenis

- 8) Eddy currents

- 9) Curie Point

- 10) Magneto-Striction.

- 11> Soft & Hard magnetic Materials.

- (a) self magnetic material

- (b) Hard magnetic material.

Magnets

- 1 Permanent Magnet

- (current induced magnetism)

- · Magnetic dipoles are found to exist in magnetic materials.

- · A magnetic dipole is a small magnetcomposed of north & south poles instante of positive & negative charges.

N S F

- Magnetic forces are generated by moving electrically charged particles. These forces are in addition to any electrostatic forces that onay already exist

- field, which is represent in distributed field, which is represented by imaginary lines. These lines also indicates the direction of the force.

Magnetic field is generated by passing . Magnetic field is generated by passing current I through a coil of length current I through a coil of length 'L' and number of turns 'n', then the

magnetic field.

Susceptibility = (TX) = M ; B = MOH + NOM

Types of Magnetism: - Xm = Mn-1.

· A material is magnetically characterized based on the way it can be magnetized

. This depends on the material's magnetic susceptibility.

There are 3 basic magnetisms,

- 1 Dia-magnetism

- (2) Para magnetism

- 3 Fermo-magnetism.

Dia - magnetism . -

- · Very weak; exists only in presence of an external field, non-permanent

- . The induced magnetic moment is very small and the magnetisation (M) direction is

Design of a 3-bit Binary to Gray code conventer.

$$G_{13} = B_{2}$$

.

$G_{12} = B_{3} \oplus B_{2}$ .

$G_{11} = B_{2} \oplus B_{3}$ .

Design of a 3-bit Gray-to-Binary code roug conventen: --> The "/p is a 4-bit gray code & 0/p is a 4-bit bindry. -> There are 16 possible combinations of 4-bit gray Enprof and all of them are valid Gray 0 B 0 B 0 . 0001 0 1 0 1 3 0 30 ----1 9091 ---1 1 0 i i ----- 1 0 1 ubit gray - Binary B3 = G2.

- 1) Design of Ubit Binary to Gray.

- 2) Design of 4 bit Gray to Binary.

- 3) Design of Abit binary to Ex-8.

- 4) Design of Ubit Ex-3 to binary.

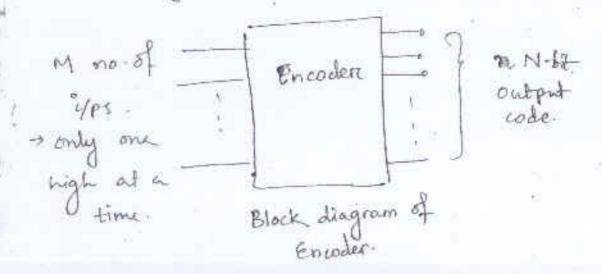

#### Encoden: -

An encoder is a device whose inputs are decimal digits on alphabetic characters and whose outputs are the coded representation. of those inputs.

- -> combinational logic circuit that performs.

The 'reverse' operation of the decoder.

- -> The opposite of decoding process is called encoding

#### Octal to Binary Encoder: -

> This a 8:3 line encoder. It accepts 8 input line and produces a 3 bit output

| code -         | Truth Table     |

|----------------|-----------------|

| Octal Digits   | Binarry         |

| Do \           | A2 A1 A0        |

| D <sub>2</sub> |                 |

| P <sub>3</sub> | → 100<br>—→ 101 |

| D <sub>5</sub> | 110             |

| D <sub>3</sub> | → 1 1 1         |

$$A_2 = D_4 + D_5 + D_6 + D_7$$

$A_1 = D_2 + D_3 + D_6 + D_7$

$A_0 = D_1 + D_2 + D_5 + D_7$

Logic Diagram

|                |    |     | B | inar | (D) | 201 |

|----------------|----|-----|---|------|-----|-----|

| Decimal if     | PS |     | Α | B    | c   | D   |

| Do             |    |     | 0 | 0    | 0   | ()  |

| P              |    |     | 0 | 0    | 0   | 1   |

| Ω              |    |     | 0 | 0    | = 1 | D   |

| D <sub>2</sub> |    |     | 0 | 0    | . 1 | -   |

| 9              | 3  |     | 0 | 1    | (   | 2 1 |

| Dy             |    | - i | 0 | 1    | C   | 2   |

| D <sub>5</sub> |    |     | 0 | . 1  | 1   | 0   |

| D <sub>6</sub> |    | 3   | ٥ |      | 1   | (   |

| D <sub>2</sub> |    |     | 1 | (    | 0 0 | 0   |

| Da             |    |     | - |      | J 1 | 0   |

Truth Table

A = D8+D7, B = D4+D5+D6+D7.

C = D2+O3+D6+D7, D = D1+D3+D2+D2+D3+D4+D4

+ D9

There is no explicit input for a decimal O. The BCD output is 0000 when the decimal inputs 1-9 are all

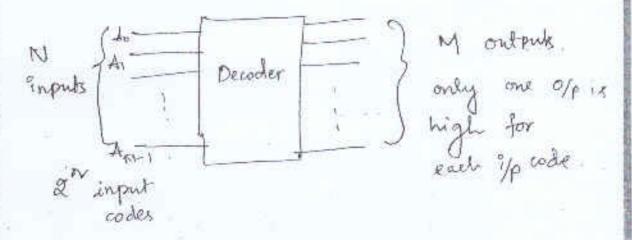

#### De coder : -

A decoder is a digital circuit that converts an NI-bit binary E/p code into M-0/p lines such that only one 0/p line is activated for each one of the possible combination.

- 1 2:4 line decoder

- (2) 3:8 line de coder

| (1) | 254 |     |    |    |     |

|-----|-----|-----|----|----|-----|

|     | An  | Do  | D, | Da | D3  |

|     | 0 0 | 1   | 0  | 0  | 0   |

|     | 01  | 0   | 1  | 0  | 0   |

|     | 10  | 10  | 0  | Ü  | 0   |

|     | ( ) | 1 0 | O  | 0  | 1 2 |

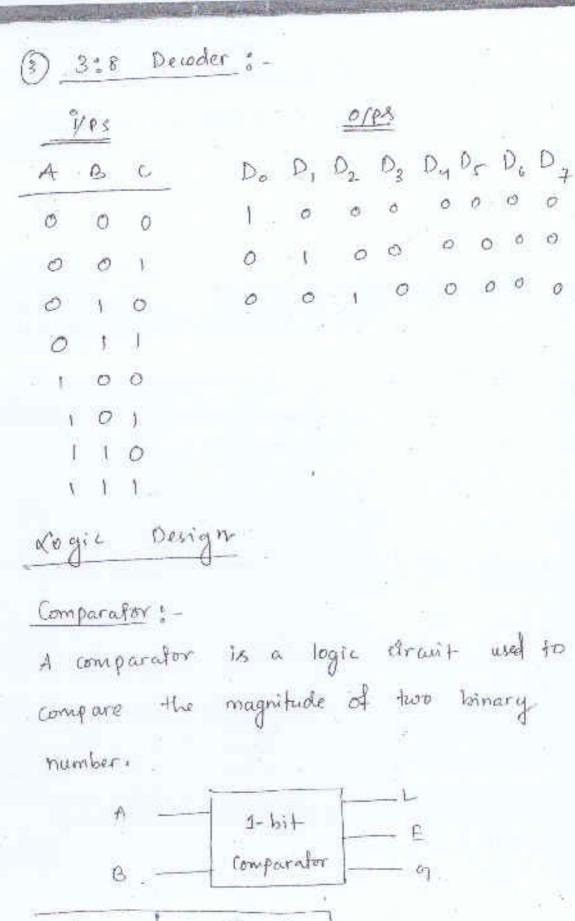

| Ao Bo | L | £ | 9 |

|-------|---|---|---|

| 0 0   | 0 | 1 | 0 |

| 0     | 1 | 0 | Ō |

| 1 0   | 0 | 0 | 1 |

| 1 1   | 0 | 1 | 0 |

## 2 bit magnitude Comparator: -

Net the two 2-bit numbers be = A = A = A = A

and B = B, Bo

D

0

$$A > B \longrightarrow G = AB$$

$$A < B \longrightarrow L = \overline{A}B.$$

$$A = B \longrightarrow E = A \textcircled{B}B.$$

2-bit magnitude comparator:

act the 2 bit number A = A, Ao and

B = B, Be

1.  $A_1 = 1$  and  $B_1 = 0$ , then  $A > B \supseteq T$ 2. If  $A_1$  and  $B_2$  coincide and  $A_0 = 1$  and  $B_0 = 0$ , then A > B. So the logic expression for A > B is  $C_1 = A_1B_1 + (A_1 \bigcirc B_1) A_0B_0$

1. If A = 0 and B = 1, then A < B or 2. If A, and B, are egged and A0=0 and Bo = 1, then ACB is.

ALB: L = A,B, + (A, OB, ) AOBO.

1. If A, and B, coincide and if Ao & Bo coincide then A=B . So the expression for A=B; E= (A10Bi) (A00Bo).

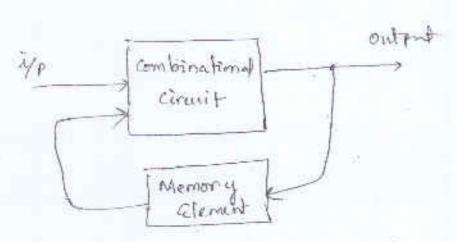

### Sequential Circuit

Block diagram of sequential circuit

The output of the s'equential circuit depends on not only the present yp but also the past 0/p & 1/p of the system.

=g:- counter, shift registers

# combination of

In combinational che,

the output variables at

any instant of are

dependent only on the

present by variables

- 2) memory unit in ( onet required in combinational circuit

- Decause the delay because the irr response to delay be in response to propagation. delay of gates only.

D combinational cut are care easy to design

### Sequential circuit

- O In sequential ckt, the of variables at any instant of time are dependent of only on the present is variables, but also on the past history of the system.

- (2) Memory unit is required to store the past history of the input variables in sequential circuit

- 3 Sequential ckt are Slower than combinational

@ Sequential out and comparatively harder to design.

# "classification of Sequential circuits: -

- 1 Synchronous sequential circuit

- 3 Asynchronous

### Synchronous Seg. ckt !-

The seg-ckt which are controlled by a clock are called synchronous sequential ckt.

These okts will be active only when clock signal is present.

Asynchronous Sequential of -

The conjunct which are not controlled by a clock are called asynchronous sequently cost

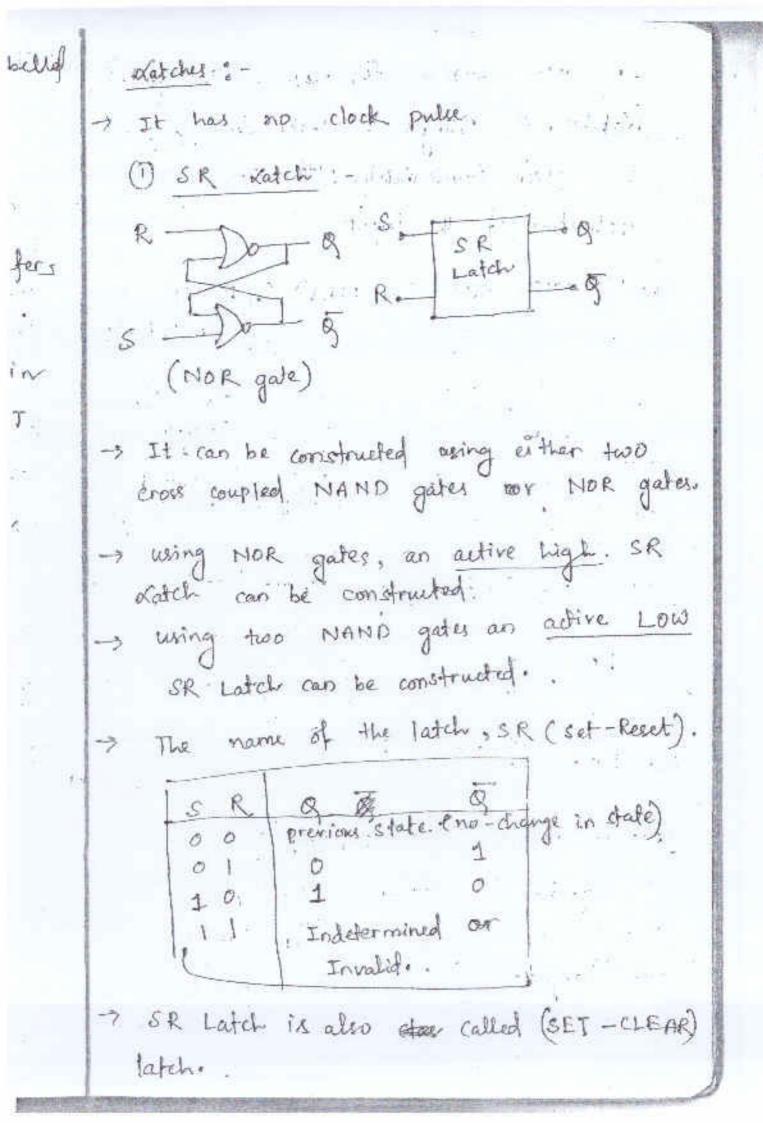

Do Latches @ flip flops.

(a) sr (b) gr (b) Jr

(0) D

(d) T.

- -> flip-flop are the basic building block of the sequential circuit.

- -> A flip flop 1/p has to pulsed momentarily to cause a change in the flip-flop ofp. and the op will remain in that new State even after the 4p pulse has been removed. This is the flip flop's memory Characterstics.

-> flip-flop acts as a storage device.

It stores 1 when go/p is 1; stores o' when & off is o.

-> flip flops are the fundamental components of Shift Registors & counters.

> (Normal O/p) Wes (LE) & > (Inverted %)

-> A flip flop can have one or more i/ps. The yp signals which command the flip flop to change state are called excitation.

( ky a 1 ckd

clock

trolled Sequente of & &.

B → normal O/p.

- -> The state of the flip flop always refers

to the state of the normal ofp (Q).

- when gil, The ff is said to be in high state or logic 1 state or SET.

- when \$ = 0. The ff is said to be in Low state or degic 0 state or RESET state corr elear state.

In more complex flip-flops, called gated datches, the changes of state does not take place immediately after the application of the inputs.

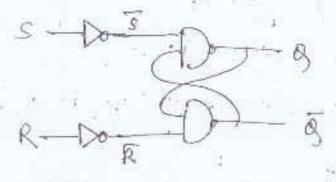

The NAND gate (CC-R Latch) (Active: 1000

S.R Latch):

S.R Latch):

S.R Latch):

S.R Latch):

S.R Latch):

Report

Report

No change.

5-R Latch (active high NAND Latch):

Gated Latches (Clocked flip flops):-

asynchronous latches. The 0/p can charge state any time to 3/p conditions are changed.

-> A gated S-R latch requires an teo Enable (EN) \*1/p. It's S & R /ps will control the state of the flip flop only when the enable is High. -> When, the enable is LOW, the yps become ineffective and no changes of state can take place. -> The enable 1/p. may be clock. So a gated S-R latch is also called a clocked S-R latch or Synchronous S-R Latch. -> This types of Nip-flops are respond to the Changes in inputs only as long as the clock is HIGH; these types of flip-flops are also called level triggered flip-flogs. HAND -En

#### Truth Table: -.

| En  | 5 'R  | Qn. | Spr+1 | State:  |

|-----|-------|-----|-------|---------|

| 1   | 0 0   | 0   | 0     | No char |

| 1 1 | 01    | Ò.  | 0     | Reset   |

| 1 1 | 1 0   | 0   | 1     | set-    |

| 1   | 1 1   | 0   | ×. ×  | Invalid |

| 0   | × × · | 0   | 0     | No chan |

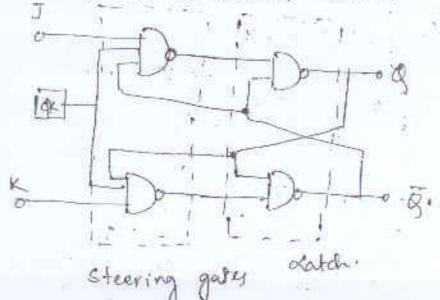

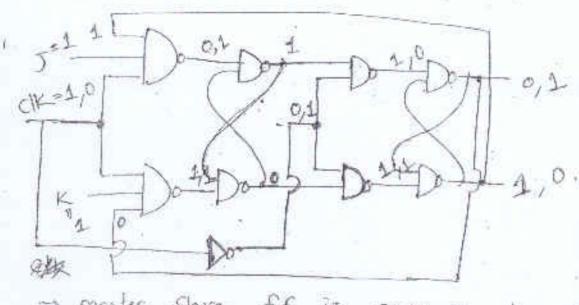

### JK-flipflop:-

→ JK flip flop is called an universal flip flop because the flip flop like T-ff, D-ff, se-flip flop can be derived from it

Truth Table 1999 1 10 00 clock J K.  $Q_{n+1}$ :  $0 \times X$   $Q_n$ .  $1 \times X \otimes Q_n$ . 1 1 -> Bm > Togethe - S -> Race State > Around Condition

characterstics table

| J  | K | 9, | 1 gn+1 |

|----|---|----|--------|

| 0  | 0 | 0  | 0      |

| ,0 | 0 | 1  | 1      |

| 0  | 1 | 0  | 0      |

| 0  | 1 | 1  | 0      |

| 1  | 0 | 0  | 1      |

| 1  | 0 | 1  | 1      |

| 1  | 1 | 0  | 0      |

| 1  | 1 | ,  | 1      |

Bn+1 = Jan + Kan. -> characterstics Equation.

Lip Hop s P-flip

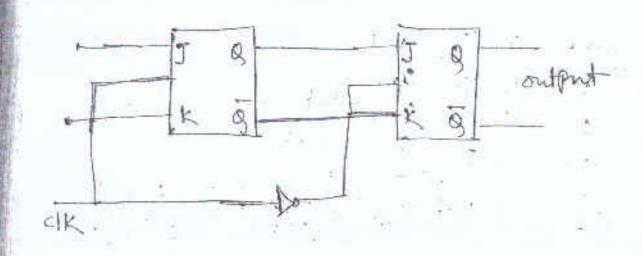

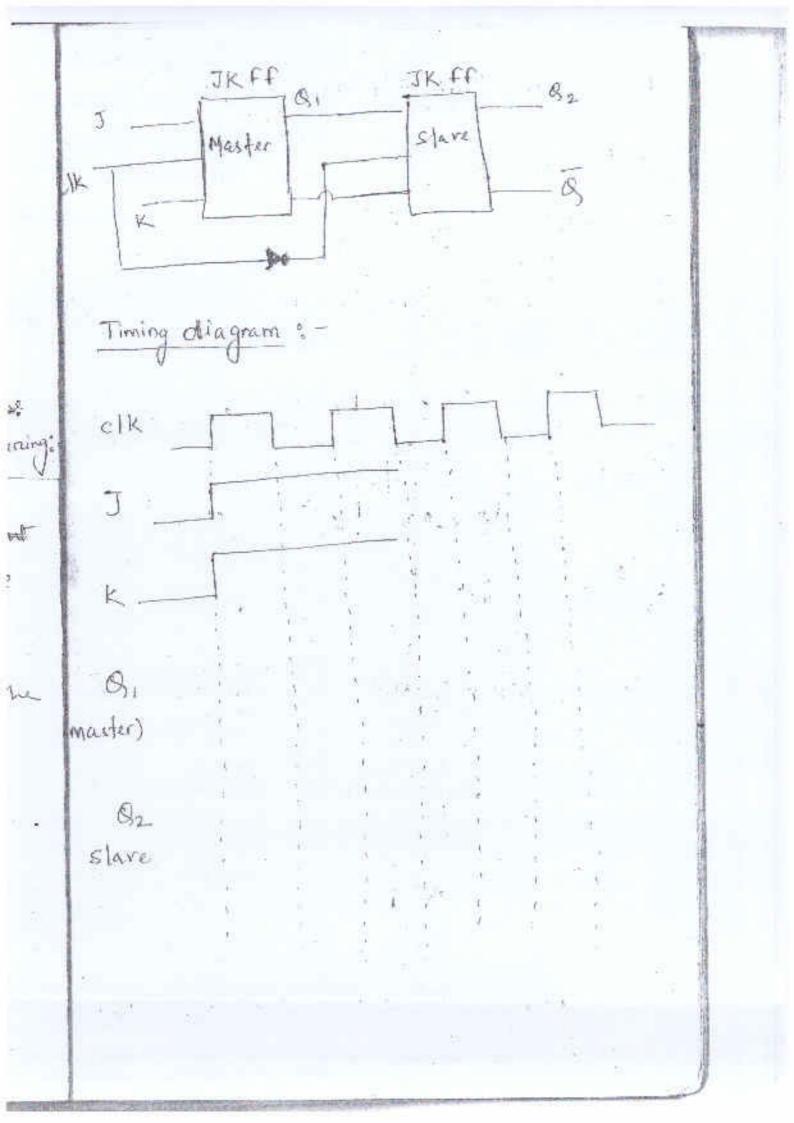

# Master-Slave JK Flipflop: -

State the necessity of clock and give the concept of level. clocking and Edge triggering:

- and foutput circuit to get a single external signal:

- output.

muster - slave flip flops: -

- -> master = slave (on) pulse traggered flip flop contains two flip flops

- Toggling is a controlled phenomenon.

\* Master slave flip flop is same as

-re Edge triggered flip flops.

> Racing is due to feedback.

> we add another level.

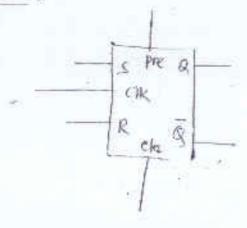

clocked SR-flipflop with preset of clear

inputs :-

B i.e to 1.

clear is used to clear the output(Q) to clear preset & 0 no change . 11 no effect If the clear & present is activated on -Ve logic then the block diagram will be, 5 0 UK Application of the flop: -. 1 used for data storage (E) transfer of data. (3) frequency Division. @ counting 6 Parallel to Series In Series to Parallel Convension

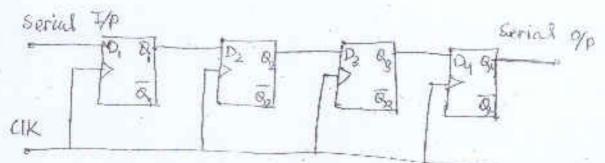

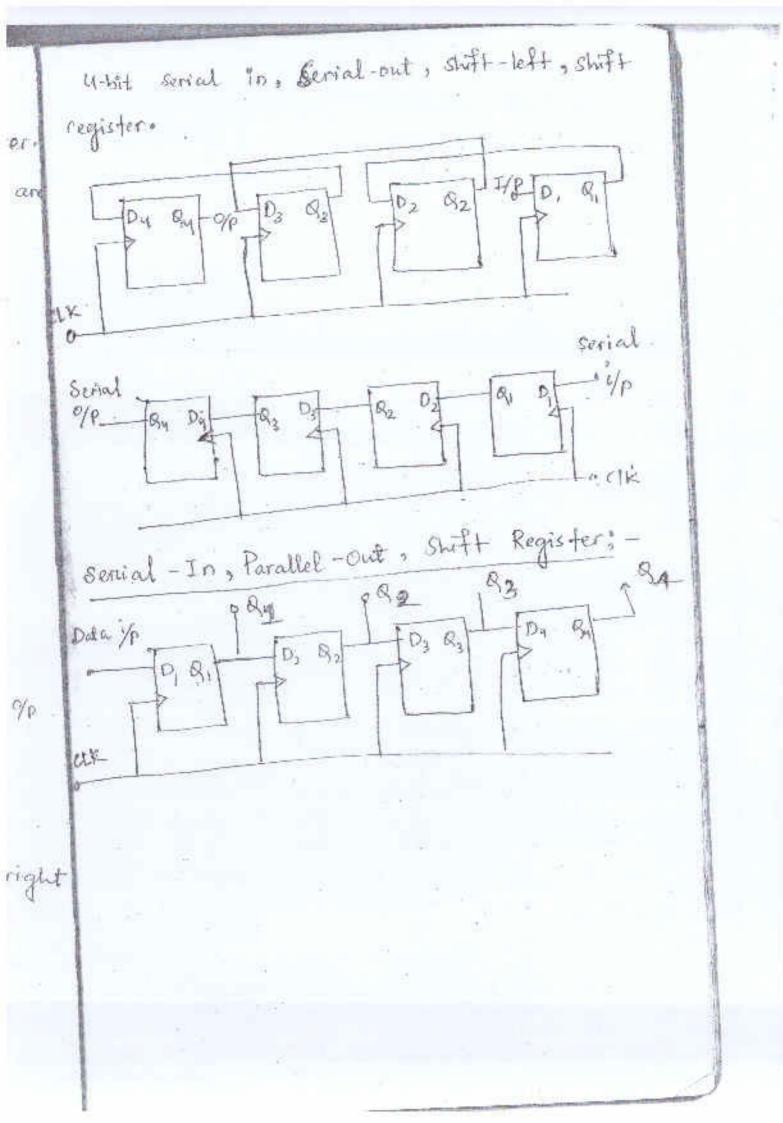

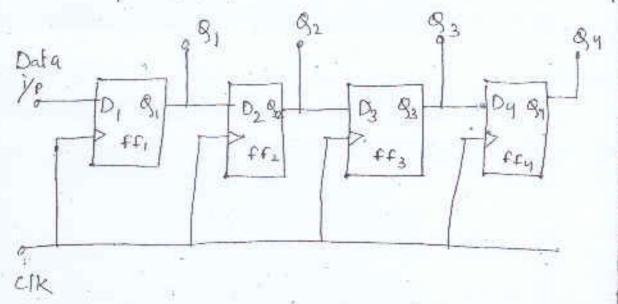

4-bit Serial-in, serial out, shift right Shift register.

In this type of register, the data hits are entered into a register serially, but the data stored. In the register is shifted out in panallel form.

U-bit Serial in, Parallel-out

Parallel In , Servial-Out (PISO) Shift

In a parallel "m, serial-out shift register the data bits are entered simultaneously into their respective stages on parallel lines. but the data bits are transferred out of the register serially, i.e bit by bit basis over a single line.

When Shift/LOAD = 0, gates G12, G14 are enabled to allowing the data input to appear at the D inputs of the respective fifs., therefore clata is inputted in one

The OR gates allows either the normal shifting operation or the parallel data entry depending on which AND gades are depending on which AND gades enabled by the level on the shift shop input

Parallel -in, Parallel-out shift Register: A SAG GB BAG C Beg D BO LID OF LD OF LD OF 4-bit Parallel in-Parallel

the date to their respectiv & but the dai

of the register

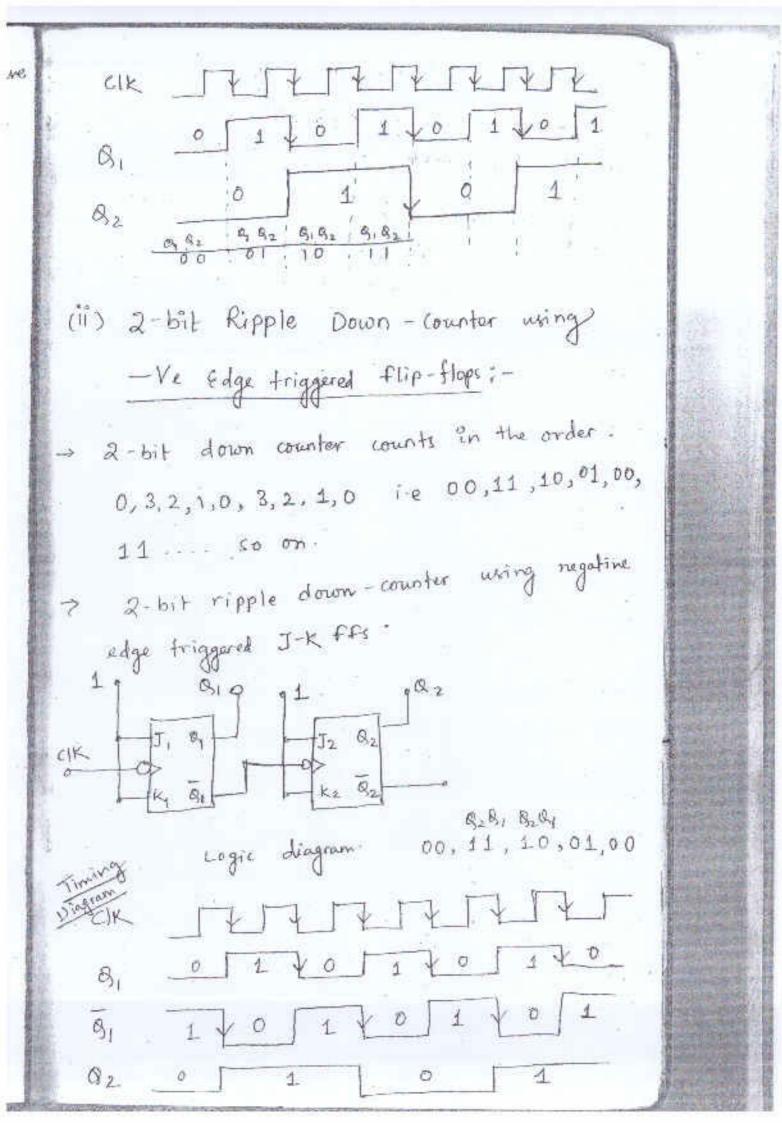

Counters ire 1 Asynchronous counter/Ripple Counter. ) 2) Synchronom counter. dive me Synchronous Counter Asynchronous Counters 1. In this type of 1. In this type of counter Ffs are connected in such a way counter there is no ma that the output of 1st fi connection b/w the entry O/p of the 1st FF drives the clock for the 2nd ff, the opp of the 2nd the and clock input of next ff h so on. clock of the third & so input ster : 2. All the sts are 2. All the ffs are not Op on clocked simultaneouslyclocked simultaneously. 3 3. Design & Emplementalin 3. Design & implementation becomes tedions and Is very simple even complex as the number of for more number of status increases. states. Mel 4. Main drawback of these (y.) Since clock is applied to all the ffs simultaneously counter is their low the total propagation des speed as the clock is delay is equal to the propagated through on propagation delay of only mumber of ffs before it reaches the last of one of Heme they are faster

# Counter - (i) UP (ounter - )(ii) DOWN (ounter.

#### (i) UP counter :-

An up-counter is a counter which countes on the upward direction i.e. o, 1.2, 3 ---- NI.

#### cin Down counter :-

A down-counter is a counter which counts in the downward direction, the N, N-1, N-2, N-3, ....., 1,0

State:-

Each of the counts of the counter is called the state of the counter.

#### Modulus of the counter: -

The number of states through which the counter passes before returning to the starting stage is called the modulus of the counter.

-> so the modulus of the counter he equal to the total number of distinct states (our)

- · (i) 2-bit counter

- (i) 3-bit counter

- (iii) 4- hit counter.

- (9x) 5-bit counter.

- (i) 2 bit counter: -

- -> It has 4-states, it is called make counter.

- -> It requires 2 ffs.

- $\Rightarrow$  The number of states =  $2^2 = 4$  states.

- → It divides the 1/p clock signal frequency by 4, therefore, it is also called a divided by 4- counter.

- (ii) 3-bit counter: -

- $\Rightarrow$  A 3-bit counter uses 3 ffs and has  $2^3 = 8$  States.

- -> The number of states = 8.

- -> It divides the 1/p clock frequency by 23

Note: In general, an n-bit counter will have a n-ff and 2" states, & divides the "/p frequency by 2". Hence it is a divide by -2" counter.

== q = MOD-2 Counter

How many bit's FFs it require?

MOD-4 counter, mod-5, mod-10.

How many ffs it require?

- -> mod-2 counter & mod-5 counter can be combined to get a mod-10 counter.

- -> mod-5 counter & a mod-4 counter can be combined to get a mod-20 counter.

## Asymptonous Counter: -

## Combinational dagic Circuits

- A digital circuit is combinational of it's ordered is depending on Exputs (i.e the present of).

- -> The combinational logic circuit is memory less.

- -> This logic circuit deals with the method of combining basic gates to get the desired

- Elements of Combinational dogit :-

- 1 diteral 3 Sum term 5 Products of

2 Product term 9 Sum of products

- @ Minterms @ Maxterms

- (8) Canonical forms, (6) Canonical sum of products

- (10) Canonical froduct of sums

- (1) Sum of minterms.

- (12) Product of maxtenns.

## Combinational dogic Circuiti-

- 21) Give the concept of combinational logic circuit

- 2.2) Half adder circuit and verify its function using truth table

- 2.3) Realize a Half-adder wring NAND gales only and NOR gater only

- 2.4) full adder circuit and explain its operation with T-T

- 2.5") Realite full adder using two half adder and an ex-gale & write to 1.

2-9) Operation of 4:1 max & 1:4 demux. tput is 2.8) working of Binary - Decimal Encoder & 3x8 checoder. Coorking of two bit magnitude compartur. Chapter-1 D K map for 2.3,4 Variable, simplification of sop and pos dogic expression. wing K-MAP

### Degital Electronics

8.1) Name 4 types of number system and writes.

2) 3) 6) Find the 21's complement of (101011101),

- 3) Design Ex-OR gate using NAND gate

- gutes in write it's truth Table audwith

- 5) Define demorgan's theorem & write it's expression in 223-variable form

- Design Hold Adder with neat logic dingram.

- 2) Design 4:1 multiplexur with nent logic diagram

- Reduce.

Solve the given expression

by using K-map and desiry draw it's

logic diagram.

f(A,B) = AB + AB + AB